# Integra FLEX

System Description

### Disclaimers

TimeTrack, Background DSP, DataTool, Mixed-Signal Workshop, IG-XL 5.0, IMAGE, and J750 are Trademarks or Register Trademarks of Teradyne, Inc. All other trademarks are those of their respective owners.

©2002 Copyright Teradyne Inc. This document may not be reproduced, in whole or in part, without the written permission of Teradyne, Inc., 321 Harrison Avenue, Boston, Massachusetts 02118 USA

# **Table of Contents**

| Integra FLEX – Revolutionizing ATE Solutions | 7 |

|----------------------------------------------|---|

| Manufacturing Utilization                    |   |

| Executive Summary                            |   |

| Manufacturing Capacity                       |   |

| Time-to-Revenue                              |   |

| Conclusion                                   | 8 |

| Section 1: IntegraFLEX Overview                                                 | 11 |

|---------------------------------------------------------------------------------|----|

| Integra FLEX Objectives                                                         |    |

| Architectural Feature Overview                                                  |    |

| Tester-In-The-Testhead                                                          |    |

| Universal Slots                                                                 |    |

| Mixed-Signal Clock Architecture                                                 |    |

| Instrument Control                                                              |    |

| Test Computer/TCIO Bus                                                          |    |

| Pattern-Controlled Analog Instrumentation                                       |    |

| Multi-site Concurrent SOCTest                                                   |    |

| Direct Digital Synthesis Clock Per Instrument                                   |    |

| Pattern Generator Per Instrument                                                |    |

| Pattern-Controlled Analog Instruments                                           |    |

| Instrument Triggering                                                           |    |

| Per Instrument PPMU                                                             |    |

| Multiple Time Measurement Units                                                 |    |

|                                                                                 |    |

| Multi-Bank Capture Memory                                                       |    |

| High-speed Back-end Data Move Bus<br>Multi-Level Signal Processing Architecture |    |

| Multi-Level Signal Processing Architecture                                      |    |

| Minimization of Shared Resources                                                |    |

| Digital Capabilities for the SOC and DFT Worlds                                 |    |

|                                                                                 |    |

| Innovative Heritage                                                             |    |

| Section 2: Meeting Test Floor Objectives       | 19   |

|------------------------------------------------|------|

| Enhanced Manufacturing Utilization             |      |

| Per Pin Resources                              | 19   |

| Configuration Flexibility                      | 19   |

| Increasing Manufacturing Capability            | 21   |

| Elimination of Bottlenecks                     | 21   |

| Non-Pipelined Test Computer/Test System Link   | . 21 |

| Background DSP/Real-Time Processing Capability |      |

| Universal Instrument Slots                     | . 21 |

| Minimized Shared Test System Resources         | . 22 |

| DIB Access                                     | . 22 |

| Pattern-Controlled Analog Instruments          | 22   |

| Section 3: Improving Time-To-Market                    | 23 |

|--------------------------------------------------------|----|

| Unrestricted Test Development                          |    |

| Precision Synchronized Cross-Domain Debugging          |    |

| Integrated Tools                                       |    |

| Simplified Docking and Production Integration          |    |

| Integra FLEX/Catalyst Prober Interface Configurability |    |

| Integra FLEX/Catalyst Handler Interface Configurability | 24 |

|---------------------------------------------------------|----|

| Integra FLEX/J750 Interface Configurability             | 24 |

| Handler/Prober Communications                           | 24 |

|                                                         |    |

| Section 4: Multi-Level Test Development: IG-XL 5.0      |    |

| Key Objectives                                          |    |

| Multi-level Programming Capability                      |    |

| Device-centricTest Development                          |    |

| General DataTool™ Overview                              |    |

| Pin Map                                                 |    |

| Pin Map<br>Channel Map                                  |    |

| Device Spec Sheet                                       |    |

| Timing and Format Setup                                 |    |

| DC and Pin Levels                                       |    |

| PDE-Procedure Development Environment                   |    |

| Test Instances – Design Once, Re-use Many Times         |    |

| Standard Test Templates                                 |    |

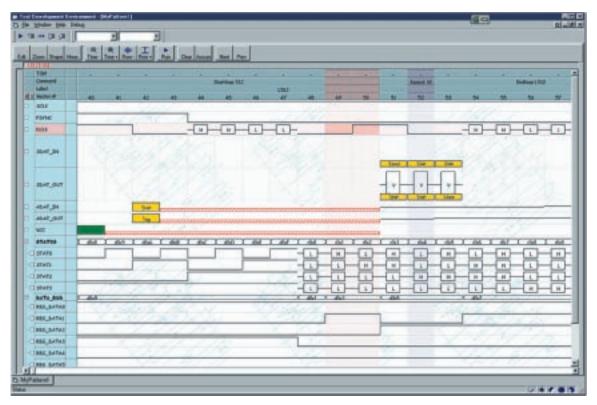

| Test Debug Environment                                  | 30 |

| Digital                                                 | 31 |

| Pattern Tool II                                         |    |

| Test Instance Editor                                    |    |

| Digital Waveform Display                                |    |

| Mixed-Signal SOC                                        |    |

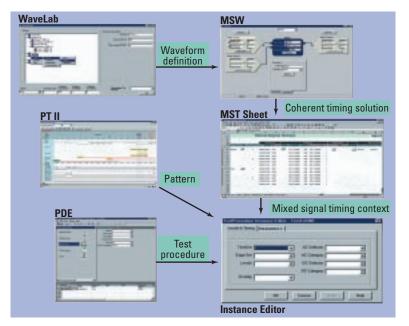

| Test Development Flow                                   |    |

| WaveDesigner                                            |    |

| WaveScope                                               |    |

| Mixed-Signal Workshop (MSW)                             |    |

| Putting it All Together                                 |    |

| Background DSP Environment                              |    |

| Native Multi-site Capabilities                          |    |

| Virtual Test                                            |    |

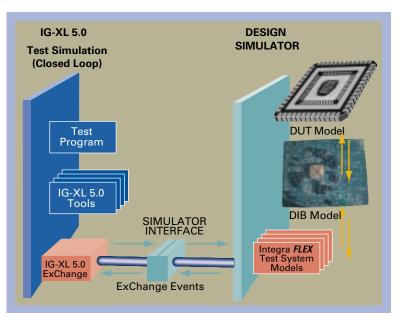

| VX Test Simulation Software                             | 35 |

| Digital VX                                              | -  |

| Mixed-Signal VX                                         | 37 |

| qVX                                                     | 37 |

| Design-to-Manufacturing Support                         | 37 |

| Section 5: Instrument Description and Specifications | 39  |

|------------------------------------------------------|-----|

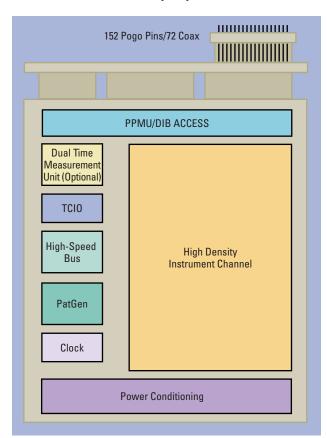

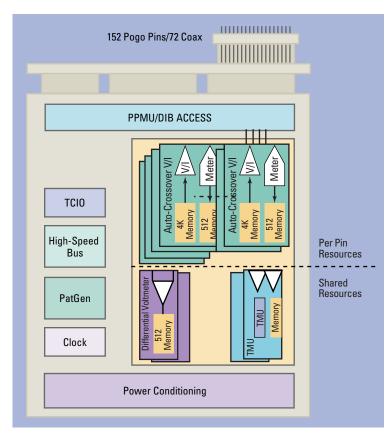

| Common Instrument Functionality                      | 39  |

| Instrument Triggering                                | 39  |

| Per Pin Measurement Unit                             |     |

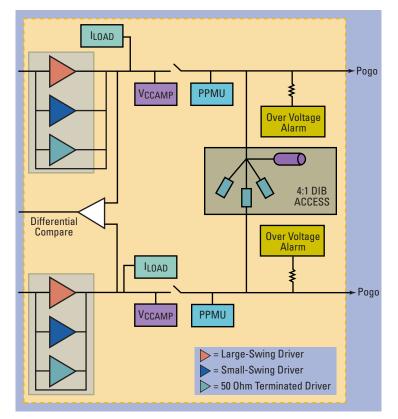

| DIB Access                                           |     |

| Direct Digital Synthesis Optical Reference Clock     | 40  |

| Pattern Generator                                    | 42  |

| Logical PatGens                                      |     |

| PatGen Failure Reporting                             |     |

| Parameter Set Memory                                 |     |

| Capture Memory                                       |     |

| High-Speed Back-end Data Bus                         |     |

| TCIO Bus                                             |     |

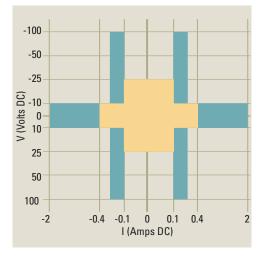

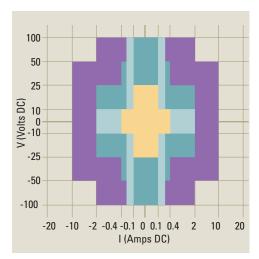

| DC Instruments                                       |     |

| Common Functionality                                 |     |

| V/I Modulation                                       |     |

| Time Measurement Unit                                |     |

| DC30 V-I Source                                      |     |

| DC75 V-I Source                                      |     |

| DC30/DC75 Device Power Supply/High Regulation Mode   | 51  |

| DC30/DC75 Merge Mode                                 |     |

| Special DC Instrument Mode                           | 51  |

| DC90 V-I Source                                      | 53  |

| DC Instrument Example                                | 55  |

| AC Instruments                                       |     |

| Broadband AC Instrument (BBAC)                       |     |

| VHF AC Instrument (VHFAC)                            |     |

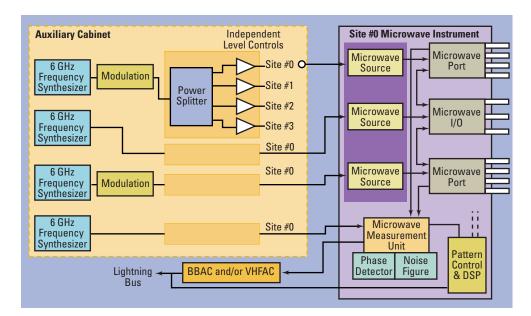

| Microwave                                            |     |

|                                                      | .01 |

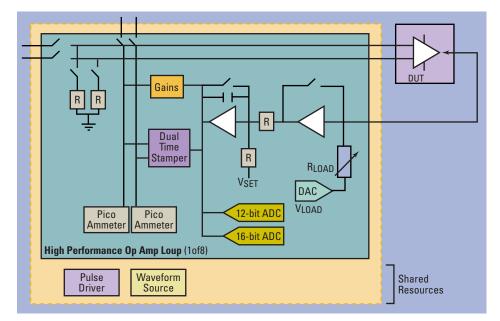

| Precision Octal Opamp Loop (POOL) Instrument6                                                 | 33        |

|-----------------------------------------------------------------------------------------------|-----------|

| Precision Octal Opamp Loop (POOL) Instrument6<br>Digital Instruments6<br>General Capabilities | <b>35</b> |

| General Capabilities                                                                          | 65        |

| Pin Electronics                                                                               | 65        |

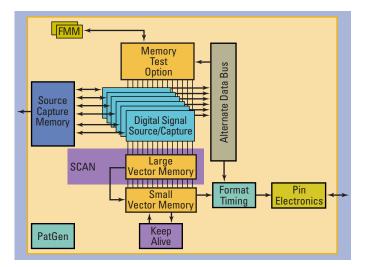

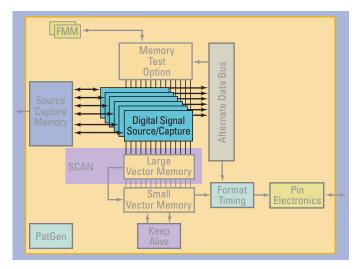

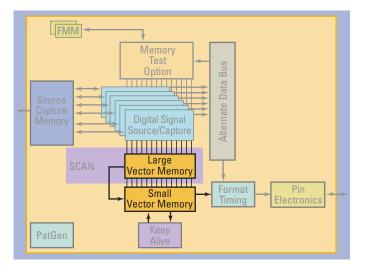

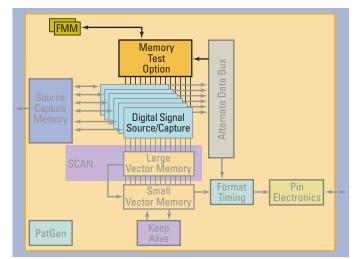

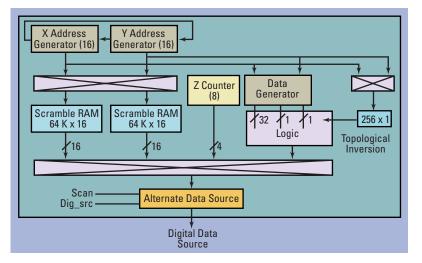

| Digital Signal Source and Capture                                                             | 65        |

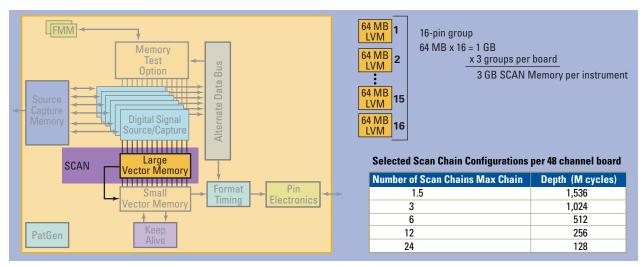

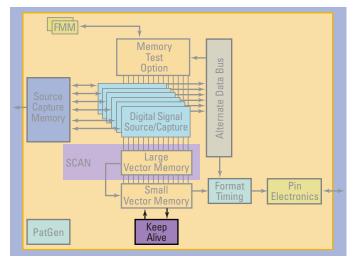

| Vector Memory                                                                                 | 66        |

| Memory Test Option and Fail Map Memory                                                        | 66        |

| SCAN                                                                                          |           |

| SCAN Flexibility and Speed                                                                    | 67        |

| SCAN Broadcast                                                                                | 67        |

| Keep-Alive Function                                                                           | 67        |

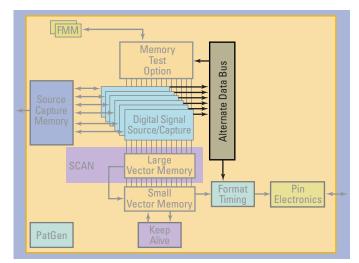

| Alternate Data Bus                                                                            | 68        |

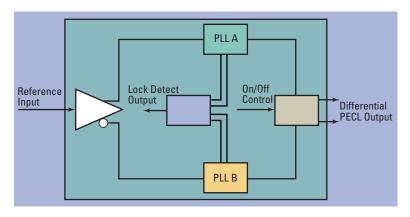

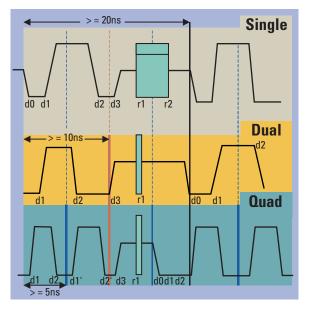

| Low-Jitter Clock Source — PicoClock Module6                                                   | 68        |

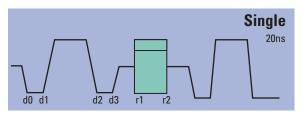

| Single Mode                                                                                   | 71        |

| Modes, Tsets, and Edgesets                                                                    | 71        |

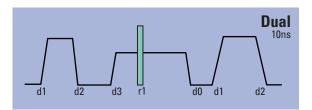

| Dual Mode                                                                                     |           |

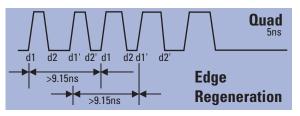

| Quad Mode                                                                                     |           |

| Appendix 1: Worldwide Support                                                                 | '3        |

| Appendix 2: Contacting Teradyne7                                                              | '7        |

# **Executive Summary**

# Integra FLEX – Revolutionizing ATE Solutions

Device manufacturers are under increasing pressure to improve overall resource utilization and time-to-market to compete with the pace of technology change and falling device ASPs. This pressure is driving manufacturers to rethink the technology they purchase to manufacture and deliver their products to market. Whether Teradyne is working with Product Management, Test Engineering, or Device Manufacturing, they each share the economic goals of speeding overall device development time, improving utilization of equipment and resources, and providing the required performance to support device development and introduction.

Integra FLEX brings to the marketplace a *revolution* in mixed-signal multi-site test with a *wide range* of instrumentation to cover a wide variety of device segments – DFT to SOC. The architectural features of FLEX will exceed market expectations for delivering improvements in performance, productivity, quality and overall test costs. How customers think about ATE will never be the same as Teradyne introduces the FLEX features — *Universal Slot Architecture, TimeTracks, Background DPS, IG-XL 5.0 software, and Performance-on-Demand* — to provide device manufacturers with new degrees of freedom. It's what you would expect from the leader in ATE solutions!

Integra FLEX was designed to address the key cost priorities of our customers:*improving manufacturing utilization, increasing manufacturing capacity, and reducing time-to-revenue.*

### Manufacturing Utilization

FLEX was designed with the explicit objective to improve manufacturing utilization of ATE. Teradyne's mechanical engineers designed the FLEX with the *Universal Slot Architecture* for configuration flexibility. Instrumentation teams designed Integrated Instruments to increase the available resources behind each pin and simplify the applications work required for device program development. Teradyne's *Performance-on-Demand model* for the FLEX provides real-time enabling of system functionality to better align required performance and device ATE costs. This "pay-per-use" model is an exciting feature developed in response to customer requests for more functional flexibility in Teradyne's ATE solutions. FLEX introduces Teradyne's Universal Slot Architecture. The FLEX test head contains 24 universal slots, meaning that any instrument can go into any test head slot (any board, any slot), whether you need digital, AC, DC, microwave, DFT test capability. This feature provides customers with the flexibility to configure the FLEX to support a wide range of device testing needs (e.g., mixedsignal, standard analog, digital, uwave, etc.) with just one configuration. The FLEX is a *tester-in-a-test head architecture*. Unlike other test platforms, which have both a test head and mainframe components, the majority of FLEX instrumentation is contained on a single channel card that inserts into one of the test head slot of the FLEX.

Improvements in manufacturing utilization are also achieved through the *Integrated Instrumentation* of FLEX. Teradyne engineers have achieved never before seen levels of integration, providing unmatched capability behind each pin in the system. For example, FLEX offers per-pin PPMU on all instruments and *DIB Access*, which allows any pin to be connected to any instrument, without applications circuitry. The suite of DC instruments provides multiple TMU and differential voltmeters per instrument. FLEX digital instruments offer new levels of integration with self-contained MTO, multiple DSSC engines, and enhanced SCAN functionality. The result is a revolution in resource availability and flexibility to support the device testing needs of our customers.

Teradyne is also introducing its new *Performance-on-Demand* option on the FLEX system. This capability allows real time enabling of key system functionality (e.g., data rate, MTO, SCAN, LVM, DSSC, etc.). These on-the-fly performance features are licensed to match FLEX capabilities with the device test requirements to improve utilization and reduce associated test costs.

# **Manufacturing Capacity**

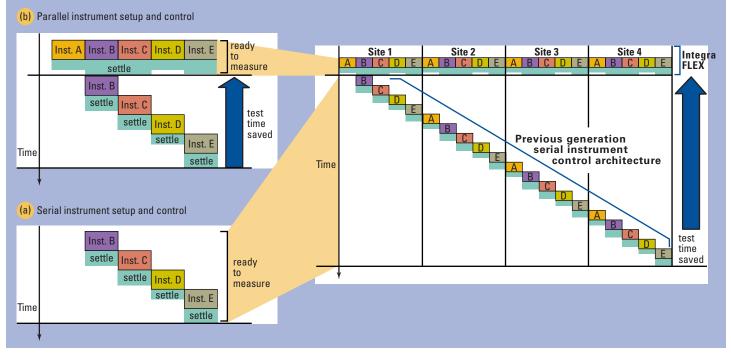

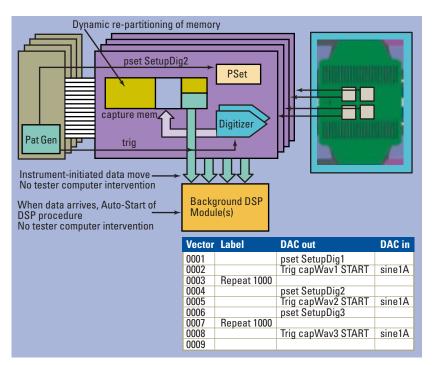

Another key design objective of the Integra FLEX was to increase the manufacturing capacity of ATE by fundamentally enhancing architectural features to achieve new levels of throughput. This expanded throughput is enabled by the *Background DSP* and *TimeTracks* architectural features of the FLEX.

The *Background DS* architecture of the Integra FLEX removes test bottlenecks that limit the throughput

performance of other ATE platforms. While other systems have shared data movement and processing resources, the FLEX has three DSP tiers and point-to-point move buses to support your device test processing. Level 1 real-time processing is always available. Here the complete signal processing is executed in the host test computer. Level 2 real-time signal processing is accomplished by the addition of up to eight (8) modular Real-Time Processors to the Integra FLEX system. Once installed, these modules are dynamically brought online as the number of parallel sites increases. These are modular boards which plug into the two system support boards and are scalable and upgradeable, based on your device testing needs. Level 3 real-time signal processing is available on-board on a per-instrument basis. The FLEX also has point-to-point move buses that connect each instrument to the test head support boards. As you move to testing more sites and more complex SOC devices you need a tester which eliminates the shared resources of moving and processing test data. FLEX was designed to eliminate shared resources and drive substantial improvements in throughput.

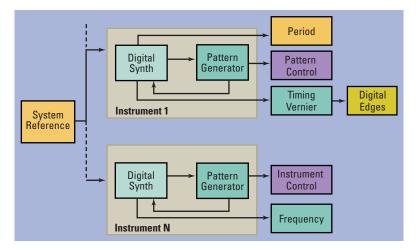

Teradyne is also introducing the *TimeTracks* architecture that is based on distributed pattern controlled instrumentation. Each FLEX instrument has a Pattern Generator that enables multi-site concurrent test capabilities, multiple time domains and direct instrument setups that are executed independently by each instrument. Precision timing control provides improved test repeatability.

# **Time-to-Revenue**

Device manufacturers are also looking to their suppliers to improve the time it takes to move from initial device concept to the release of the device to the end applications. FLEX *IG-XL 5.0* software offers device manufacturers new tools and capability to meet the increasing complexity of device technology. FLEX also leverages proven production integration solutions to simplify docking and integration into the production environment.

IG-XL 5.0 speeds test program development with reusable test program IP and zero-time parallel test. The reusable test program IP optimizes test programs developed by expert test engineers for the novice or junior engineer. Because IG-XL 5.0 is pc-based, program development can be done anywhere, anytime.

Multi-site test program development has never been faster with *IG-XL* 5.0 software. Test engineers can develop a single site program and almost instantly go to multi-site test. The user-friendly programming environment, combined with these ease-of-use features, allows test programs to be developed faster then ever before.

# Conclusion

The expanding need to improve overall resource utilization and time-to-market will drive the market to the FLEX platform and enabling technology. These architectural features are unique and offer our customers the opportunity to recognize a competitive advantage over their competitors.

Product management, test engineering, and manufacturing technicians are being drawn to the FLEX with its improved device program development tools and opportunities to lower costs through higher overall ATE utilization.

Integra FLEX offers to the market higher levels of mixed-signal multi-site test with a range of instrumentation to cover the broadest range of device segments. Architectural features of the system will enable FLEX to exceed market expectations for performance, productivity, quality, and overall test costs.

Please refer to the individual sections within this System Description, as indicated in parentheses () for more detailed information on each of these critical architectural features of the FLEX.

- Integra FLEX Hardware Architectural Features (Sections 1 and 5)

- Tester-in-The-Tester

- Universal Slots

- 24 slots accept any instrument DC, AC, Microwave, or Digital

- 22 Digital instruments maximum

- Direct Digital Synthesis Optical Reference Clock

- 29-bit DDS clock on every instrument DC, AC, Microwave, and Digital; completely independent; referenced to common precision 100 MHz system reference; <1.0pp-billion frequency ratio accuracy; generate any required clock frequency to 36 atosecond resolution; timing and phase relationship across all domains precisely known

- Redundant (Per) Instrument Functional Blocks Reduce Shared System Resources

- 29-bit DDS clock on every instrument

- Pattern Generator on every instrument; up to eight (8) PatGens per site; up to five (5) logical PatGens per system across multiple instruments – DC, AC, Microwave, and Digital

- Parameter Set memory on every instrument

- Instrument triggering from test pattern, another instrument, test computer, or DUT

- Per pin measurement unit (DC and AC instruments)

- DIB Access allows primary and secondary instrument to connect to same pin without DIB application circuitry or relays (any pin, any instrument)

- One or more Time Measurement Units (DC instruments)

- Dynamically assigned, multi-bank, capture memory

- High-speed, back-end data Move Bus; instruments initiate data move without tester computer intervention; allows simultaneous data move and instrument setup and capture of next test data

- Multi-Source Instrument Control

- All copies of instrument across all sites setup from single broadcast write command from test computer

- Pattern-controlled analog instruments setup commands within test pattern are executed by the analog instruments

- Three-Level Signal Processing

- Dynamically allocates real-time signal processing power for Background DSP or other processing as instruments and sites are added

- Level 1 Level 1 real-time processing is always available. Complete signal processing is executed in the host test computer.

- Level 2 real-time signal processing is accomplished by the addition of up to eight (8) modular Real-Time Processors to the Integra FLEX system. Once installed, these modules are dynamically brought online as the number of parallel sites increases.

- Level 3 real-time signal processing is available on-board on a per instrument basis.

- Digital Capabilities for the SOC and DFT World

- 200 MHz maximum operating speed

- edge placement accuracy of ±250 ps

- 64 Meg vector memory behind each pin

- 48 single-ended pins or 24 differential pin pairs per board

- 1,056 digital pins maximum

- three drivers per pin large swing, small swing, and 50 Ohm terminated

- MTO capture memory is 24 M deep, with 2 M Fail Map Memory

- MTO source and capture is 32 bits wide on a single board

- 3 Gbits of SCAN data available for every 16 channels that can be configured in any way needed

- SCAN Broadcast capability for parallel test economics and longer equipment lifetime

- Digital Source and Capture (DSSC) provides serial or parallel data at 16 bits wide, with the ability to chain two DSSC blocks together for 32-bit operations

- Six (6) DSSC engines per board

- · Fast keep-alive function

- Two high voltage drive pins per board

- DIB Access per four channels/pins

- PMU per pin

- per pin overvoltage/overcurrent protection that disconnects the pin electronics from the DUT on an alarm condition

### Integra FLEX Design Objectives

- Enhance Manufacturing Utilization (Section 2)

- High level of resources behind each pin

- per-pin PMU on all instruments

- DIB Access, which allows any pin to be connected to any instrument, without application circuitry

- one or more on-board Time Measurement Units on each DC instrument

- on-board differential voltmeters on each DC instrument

- dual pin high voltage driver on Digital instruments

- self-contained Memory Test and Fail Map Memory on each Digital instrument

- six (6) independent Digital Signal Source/Capture engines each with 128Mbit memory, per Digital instrument

- 3Gbit, totally configurable, SCAN data per 16 channels/pins on Digital instruments

- Keep-Alive function on each Digital instrument

- three LFO/mixers on microwave instrument suite

- on-board Real-Time processor on microwave instrument

- Universal Slots/Configuration Flexibility

- · Any instrument, any slot

- Single instrument suite can be configured that will test the majority of devices in a product mix

- A multi-site (e.g. quad) test DIB for a single device (e.g. a mixed-signal SOC) can be used on test systems configured not only for that mixed-signal SOC device, but on Integra FLEX test systems configured primarily for linear or digital/ SOC devices, with a reduction in the number of sites (i.e. dual versus quad)

- Performance On Demand (Section 2)

- On-the-fly performance and feature licensing to match Integra FLEX capabilities with device test requirements

- IG-XL 5.0 software tools

- Hardware capabilties

- DFT configuration

- Increase Manufacturing Capability (Section 2)

- Elimination of Test System Bottlenecks

- Non-pipelined test computer/test system link

- Dynamically allocated, three-level Background DSP/Real-Time Processing

- Instrument-initiated capture data moves on independent data Move Bus

- Universal instrument slots provide unprecedented test head configuration flexibilty

- Minimized shared test system resources

- DIB access connects any pin to any instrument without DIB application circuitry or relays

- Pattern controlled analog instruments

- Instrument setups executed directly by instruments

- Precision timing control provides improved test repeatability

- Improve Time-To-Market (Section 3)

- Unrestricted test development (Section 4) fully leverage test development

- TimeTrack<sup>™</sup> precision cross-domain debugging allows events from all instruments – DC, AC, Microwave, and Digital – to be precisely lined up (within 36 atoseconds) for rapid debug

- Integrated tools support design-to-test pattern translation, test simulation, and DFT (Section 4)

- Simplified docking and production integration Catalyst and J750 prober/handler interface investments are fully protected and Integra FLEX compatible

- Multi-Level Test Development: IG-XL 5.0 Environment Features (Section 4)

- Key Objectives

- Extend the J750 IG-XL 5.0 software to provide a common platform for the entire Integra family of general-purpose testers

- Provide a multi-level programming capability to accommodate a diverse development environment, and enable a shorter development time

- Provide an advanced linear and mixed-signal use model and toolset to build on the DUT-centric test development environment of IG-XL 5.0

- General Programming Approach

- Device data entry into enhanced spreadsheet

- Seamless graphical interface and code-based programming

- Test templates, elements, and procedures library

- Immediate feedback on device parameters and timing relationships definitions

- HTML help documentation generation

- Design once, re-use many times

- Standardized, familiar interface consistent with industry practice

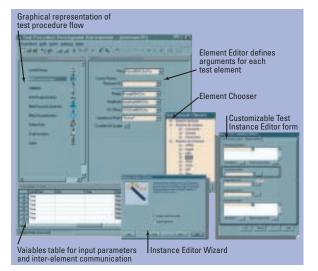

- Procedure Development Environment

- Test Instance Editor

- Standard Test Templates

- Functional (BIST, SCAN)

- Pin PMU/Board PMU (DC parametrics)

- Power Supply (ICC, Iddq)

- A/D and D/A Converter (Diff. Lin., Int. Lin, Offset Error, Absolute Error)

- MTO Embedded Memory

- Test Debug Environment

- WaveDesigner

- WaveScope

- Mixed-Signal Workshop

- Native Multi-Site Capabilities

- Multi-site testing is assumed

- Valid test program for first site (Site0) is site neutral

- Sites added by duplicating Tester Channel column and assigning instrument resources to correct channels

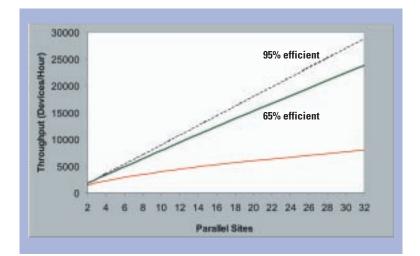

- Built-in support for up to 32 sites with 90+% efficiency

- Virtual Test

- VX Test Simulation Software

- Digital VX single seat license included with Integra FLEX

- Mixed-Signal VX

- qVX

- DataScope

- Integrated Design-to-Manufacturing Support

# Section 1 Integra FLEX Overview

# **Integra FLEX Objectives**

Teradyne's objectives for the Integra FLEX test system were to:

- Increase manufacturing capability 1) by maximizing test system throughput through the elimination of test system bottlenecks relative to the movement and processing of captured data and test instrumentation setup, 2) by the minimization of shared resources, and 3) by providing performance on demand for all aspects of the test system.

- Improve time-to-market 1) by providing a test development environment that provides a set of seamless tools suitable for both novice and experienced test programmer alike, that maximizes test development efficiency and re-use, 2) by providing a system that assumes multi-site parallel test, in both its hardware and software architectures, 3) by fully integrating the necessary

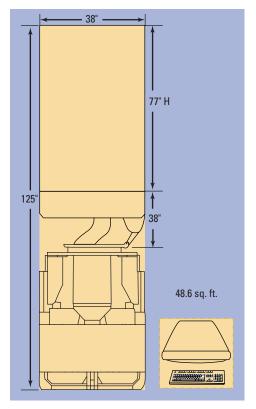

Figure 1-1: Integra FLEX test system

EDA, VX, and DFT tools, and 4) by leveraging the proven solutions and prior customer investment in existing prober and handler interfaces.

- Provide a single, scalable test platform that would deliver the lowest cost-of-test solution for both 1) functional testing of devices ranging from linear to mixed-signal and microwave SOC, and 2) driving DFT techniques for digital and SOC devices, using the same software and instrument suite.

- Enhance manufacturing utilization by 1) providing the flexibility to be configured simply and quickly to accommodate changes in device mix, emergency situations, and new device technologies, and 2) enable peaks in device test demand to be accommodated with the existing mix of test system configurations on the test floor, with no reconfiguration.

# **Architectural Feature Overview**

Prior to presenting how the Integra FLEX addresses each of these objectives, it is first appropriate to understand the key features of the Integra FLEX system and how they interact.

### **Tester-In-The-Testhead**

The Integra FLEX system has a very small footprint that is achieved by eliminating equipment bays external to the test head. and integrating the manipulator and an auxiliary equipment cabinet into a single unit. The test head itself *is* the tester. With the exception of the test computer, all of the instruments are contained within the test head. As device test requirements evolve to accommodate more complex devices, such as wireless/RF SOC devices, microwave instruments can be added to the test head and the associated frequency synthesizers may be installed in the auxiliary cabinet. An IEEE bus is integrated into the Integra FLEX so that IEEE instruments may be added to the auxiliary cabinet as well and connected to the Integra FLEX system as

needed. This modular, self-contained architecture eliminates unnecessary infrastructure costs for instruments or test capability that isn't needed. The test head is air-cooled, which eliminates the need for water cooling equipment and its attendant requirements. Figure 1-1 is a photograph of the complete Integra FLEX test system, while Figure 1-2 illustrates the footprint of the Integra FLEX system.

### **Universal Slots**

The Integra FLEX supports any instrument — DC, AC, Microwave, or Digital — in any slot in the test head. Each instrument provides its own instrument-specific signal terminations appropriate for that instrument. This allows the test head to be configured without making tradeoffs relative to multisite DIB support, provides significant improvements in signal routing flexibility, and allows rapid reconfiguration, regardless of whether instruments are removed, added, or repositioned. The test head can accommodate up to the maximum of 24 instruments (22 digital instruments maximum). The low cost universal slot test head and instrument suite of the Integra FLEX allow it to be economically configured to match varying DFT test insertion requirements across customers and the spectrum of devices deploying DFT techniques. As needs and technical requirements evolve, DFT-focused configurations of the Integra FLEX can be scaled to higher performance levels, including digital and mixed-signal functional test.

### **Mixed-Signal Clock Architecture**

Clock architectures typically rely on a master frequency synthesizer with 1 Hz resolution that is divided by a series of integer dividers to generate divide-by-N and divide-by-X clock signals for driving the Device Under Test (DUT). These two clock signals are coherent and perfectly related to one another by an integer value. The inherent problem with this approach is that division by something other than an integer value isn't possible, and, as the reference frequency increases, the difference between division by two successive integers also increases, resulting in loss of resolution. Further, it is the ratio of  $F_{\text{TEST}}$  and  $F_{\text{CLOCK}}$  that must be precisely defined so that test time is minimized, accuracy and repeatability are as high as possible, the device specifications are met, and ultimately, all four of these factors are

Figure 1-2: Integra FLEX footprint

satisfied, preferably without compromise.

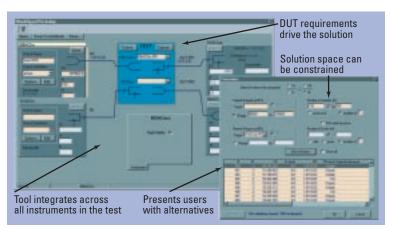

To accommodate the needs of analog, digital, and mixed-signal testing in varying test environments, the Integra FLEX clock architecture allows the test engineer to find the optimal combined solution for minimum test time, highest possible measurement accuracy, and lowest possible repeatability errors, with no compromise in device specifications. Integra FLEX represents the fourth generation of clock architecture utilizing an Optical Reference Clock per instrument. Every instrument has its own 29-bit Direct Digital Synthesis Optical Reference Clock. The 29-bit clock provides <1.0pp-billion frequency ratio accuracy. Any required clock frequency can be generated, with a resolution of 36 atoseconds. The clock on each instrument is completely independent from those on other instruments so that individual instruments can run asynchronously with respect to each other, yet all clocks are referenced to a common precision 100 MHz system reference clock. This allows all instruments - DC, AC, Microwave, or Digital — to be fully time synchronized to one another. The Mixed-Signal Workshop tool is provided that enables the test engineer to set the device specifications and to know what the limits of tester performance

Figure 1-3: Integra FLEX DDS Optical Clock Reference architecture

Figure 1-4: Time domain tool — synchronized analog and digital events

will be, *before* any tests are run. This has a significant impact on mixed-signal device testing, and can benefit digital and linear testing through improved clock accuracy and event synchronization as well.

With a clock on every instrument, timing and events can be very accurately controlled across all instrumentation. Because each clock is essentially a 29-bit counter synchronized to the master system reference, and with all starting at "zero" at  $t_0$ , the timing relationships among all clocks (instruments) are precisely known from one clock "tick" to the next, throughout every test. The time and phase for all instruments — DC, AC, Digital, or Microwave — can therefore be accurately tracked. A time domain tool is provided which allows the test engineer to look at all analog and digital events together, with resolution of all timing relationships to 36 atoseconds. This significantly reduces the effort required to

debug test programs, and increases test repeatability from run to run and test system to test system. Refer to Figure 1-4.

### **Instrument Control**

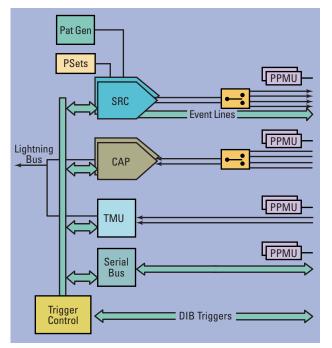

### **Test Computer/TCIO Bus**

Each instrument receives test instructions, timing, parameter set data, and other test execution data from the test computer through the Teradyne-proprietary TCIO bus. All copies of an instrument across all sites can be triggered through the TCIO bus in a broadcast mode using a single write command. This could be used, for example, to trigger 20 V/I meters each on four DC instruments, and would result in 80 simultaneous measurements, under test program control, from a single instruction.

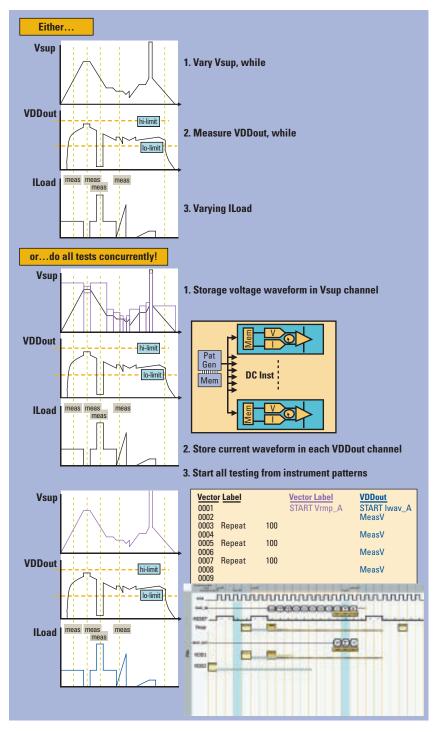

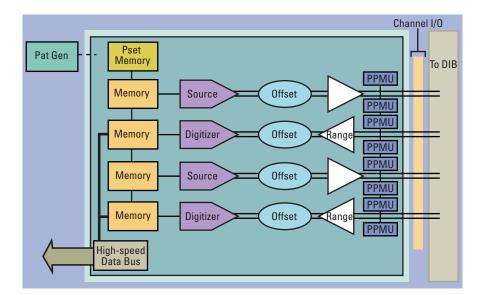

### Pattern-Controlled Analog Instrumentation

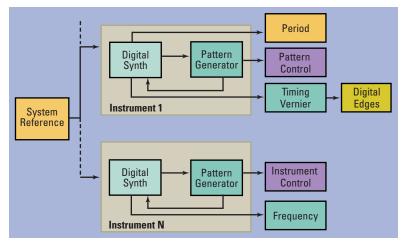

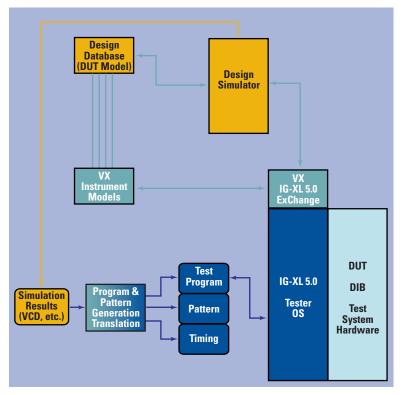

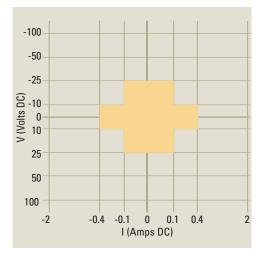

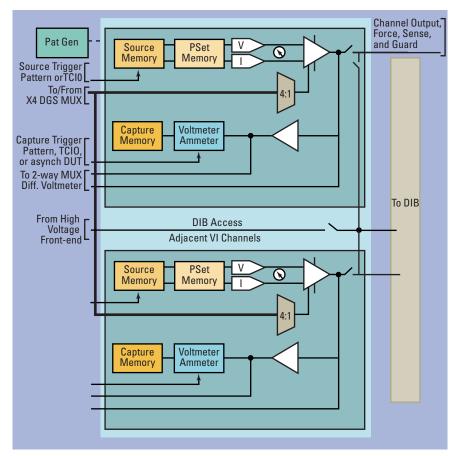

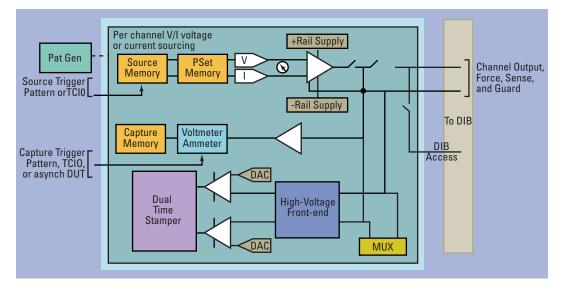

Integra FLEX achieves significant improvements in test repeatability and throughput by enabling analog instrument control directly from the test pattern. All Integra FLEX instruments - DC, AC, or Microwave have their own independent, on-board Pattern Generator, parameter set (Pset) memory, and as discussed previously, Direct Digital Synthesis Optical Reference Clock. Instrument setups are stored locally in the Pset memory on each instrument. As the pattern is executed on each analog instrument, instrument setup instructions embedded in the pattern are executed directly by the instrument, under precise timing control of the pattern. This significantly improves test repeatability, due to the precise timing control of the instruments from the pattern and their synchronization, and reduces test execution time, since instrument setup commands execute locally from Pset memory, and need not be transmitted from the test computer each time they are required. Refer to Figure 1-5.

### Multi-site Concurrent SOC Test

The Integra FLEX test system is designed to fully support multi-site concurrent SOC test when it is configured to do so. Several inherent test system and instrument features contribute to that capability, either individually, or in combination. (For detailed information on the capability of each instrument, please refer to *Section 5: Instrument Description and Specifications.*)

Figure 1-5: Integra FLEX pattern-controlled instrumentation setup

### **Direct Digital Synthesis Clock Per Instrument**

As already described, every instrument has its own on-board 29-bit Direct Digital Synthesis Optical Reference Clock, which allows any required clock frequency to be generated, with a resolution of 36 atoseconds. Because the clock on each instrument is completely independent from those on other instruments, individual instruments can run asynchronously with respect to each other, yet all clocks are referenced to a common precision 100 MHz system reference clock. This allows all instruments - DC, AC, Microwave, and Digital — to be fully time synchronized to one another. This synchronization across instruments and sites, fully supports multisite, concurrent SOC testing.

### **Pattern Generator Per Instrument**

As discussed previously, each instrument — DC, AC, Microwave, and Digital — has its own Pattern Generator (PatGen) on board driven from the instrument's clock subsystem. The PatGen controls local events and instrument setups. This means that all instruments, *including analog, are controlled from the pattern*. Patterns can therefore exercise any device, not just digital. Each instrument can run asynchronously, at an independent rate dictated by the IP core within the DUT it is to test, yet all patterns are synchronized because the instrument clocks themselves are synchronized. This capability allows the Integra FLEX to concurrently test multiple IP cores, and their interactions, under actual device operating conditions.

Up to eight (8) instruments can be combined to form a logical PatGen. Up to five (5) logical PatGens can be configured at any given time within the Integra FLEX test system. Logical PatGens can be configured across individual DUTs or multiple sites, easily accommodating test requirements as they evolve or shift abruptly.

### **Pattern-Controlled Analog Instruments**

As described earlier, the Integra FLEX analog instruments — DC, AC, and Microwave can be directly controlled from the pattern executed from the on-board Pattern Generator. Instrument setups and commands embedded within the test pattern provide precisely controlled, synchronized and repeatable execution of concurrent testing across all instruments. This concurrent test capability extends from all instruments on a single site, to all instruments across multiple sites.

### **Instrument Triggering**

Integra Flex instrument architecture is such that captures or measurements can be initiated through any one of four sources – from the test computer, from the test pattern, from another instrument, or from the DUT

Figure 1-6: DIB Access

itself. Using the DIB Access feature (refer to following section) available on all instruments, instruments can "listen" to a variety of signal sense lines for capture/measurement triggers. This capability provides significant closedloop testing abilities that enables rapid multi-site, concurrent device testing.

### **Per Instrument PPMU**

DC, AC, and Digital instruments provide PPMU functions for parallel test of continuity and leakage.

### **Multiple Time Measurement Units**

Every DC instrument has one or more Time Measurement Unit (TMU) subsystems. The TMU provides a means to tag DUT or instrument events with a very precise digital count referenced to another event. Each TMU has its own memory. The TMU 1) can look for events from the test pattern, 2) can be gated from the test pattern (i.e. "only look for events within this window"), 3) from any instrument, or 4) can accept events from the DUT itself. By providing all DC instruments have at least one TMU, parallel multi-site tests can be performed for rise/fall times, propagation delay, pulse width, frequency, and period.

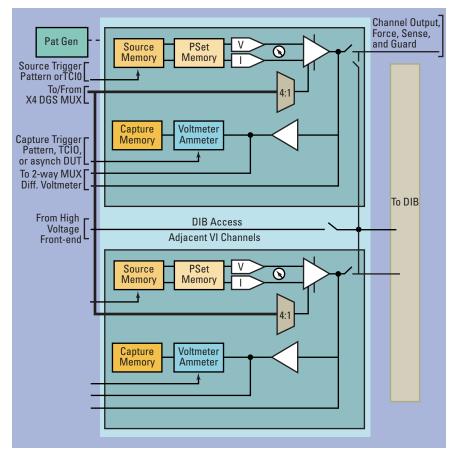

### **DIB Access**

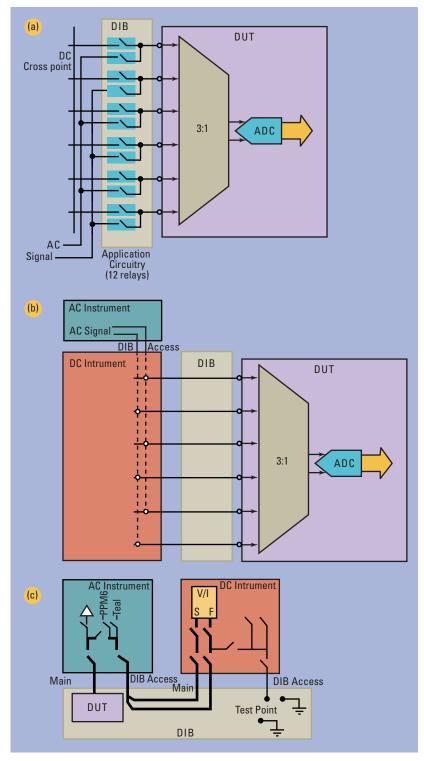

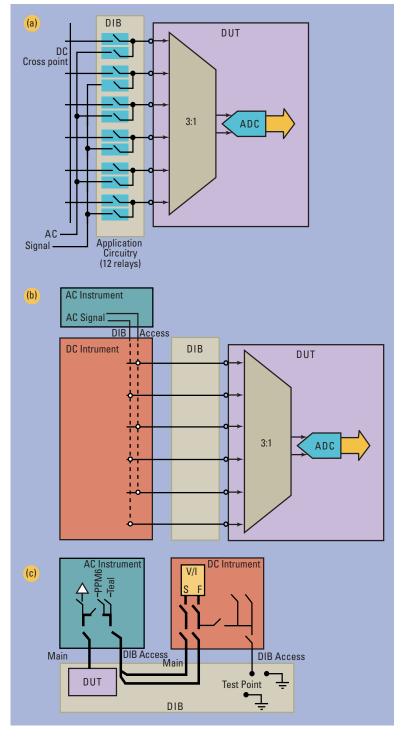

DIB Access provides the ability to route signals from one instrument to another, without requiring DIB application relay circuitry. The DIB Access feature also provides a modulation input for the DC instruments so they can be driven from the AC instruments for high power modulated source requirements. To illustrate how DIB Access works to reduce the amount of DIB circuitry required, consider the case of a DUT consisting of an ADC with a 3:1 differential multiplexer front-end Refer to Figure 1-6.

If we assume the test requirement is to measure DC resistance on all six input lines, and then inject an AC signal to all three differential inputs through to the ADC for analysis, Figure 1-6(a) depicts the application circuitry required to perform this test without the Integra Flex DIB Access feature. Twelve relays are required on the DIB to route the AC signal source to the each of the differential inputs to the multiplexer. Figure 1-6(b) shows how the relays are no longer required in the same test situation in the Integra Flex test system. The AC signal source is routed from the AC instrument to the DC instrument(s) within the instrument DIB Access subsystem(s), reducing the amount of application circuitry and the effort required to design it. Figure 1-6(c) shows how AC and DC capability are provided behind every DUT pin using the DIB Access feature.

### **Multi-Bank Capture Memory**

Each instrument has a large block of dynamically assigned capture memory, which varies in depth depending on the particular instrument. The memory is structured such that data from one capture can be moved out concurrently with the capture of data from the next test. Sufficient memory is available for storage of still additional captured data if necessary. This ability to move and capture data concurrently allows for the flexible expansion of both concurrent testing and multi-site parallel test, as needed.

### **High-speed Back-end Data Move Bus**

Each instrument has a high-speed data Move Bus that is used to move captured data off the instrument for processing. Each instrument initiates the movement of the captured data as it completes its measurements, with no test computer intervention. The Move Bus enables movement of data captured in the previous test while the instrument is being set up and data is being captured from the next test. This ability to move and capture data concurrently allows for the flexible expansion of both concurrent testing and multi-site parallel test, as needed.

### **Multi-Level Signal Processing Architecture**

Integra FLEX provides a multi-level signal processing architecture that fully enables concurrent, multi-site testing, *by incurring no parallel test efficiency penalty* as multiple sites are added. This capability is described in the following section.

### Multi-Level Signal Processing Architecture

The Integra FLEX signal processing architecture provides a significant improvement in test execution time and enables multi-site, concurrent testing, with no penalty in parallel test efficiency as multiple sites are added. This is achieved by a three-level signal processing architecture that dynamically allocates real-time signal processing power for Background DSP or other processing as instruments and sites are added. Each level is described below.

- Level 1 Level 1 real-time processing is always available. Complete signal processing is executed in the host test computer.

- Level 2 Level 2 real-time signal processing is accomplished by the addition of up to eight (8) modular Real-Time Processors to the Integra FLEX system. Once installed, these modules are dynamically brought online as the number of parallel sites increases.

Level 3 – Level 3 real-time signal processing is available on-board on a per instrument basis.

The assignment of Processor resources among the various levels is handled by the test computer and test program execution environment, with no test engineer intervention. As test data packets become available from the instruments, the Background DSP/ Real-Time Processor subsystem dynamically allocates resources as needed across instruments and across sites. If all system DSP resources are busy processing other data, the Background DSP/Real-Time Processor subsystem stores the data in a large memory that is part of the subsystem. Once a DSP resource is available, the data is moved to that resource from processing. In multi-site testing, the system will assign a dedicated Background DSP/Real-Time Processor resource to a particular test site. In this way, as sites are added and DSP resources are licensed to support them, test execution time remains virtually constant. As many as eight (8) auxiliary Background DSP/Real-Time Processor modules can be brought online as the number of parallel sites increases. The system provides sufficient flexibility and horsepower such that throughput only changes by a few percent as additional test sites are added.

### **Minimization of Shared Resources**

One of the more subtle ways that the Integra FLEX supports multi-site, concurrent SOC testing is directly related to the elimination of as many shared resources as possible in the design of the system. By providing certain redundant capabilities on each instrument, the Integra FLEX eliminates the restrictions associated with these capabilities when they are shared within a test system architecture.

As previously described, each Integra FLEX instrument has its own independent clock architecture, Pattern Generator, parameter set memory, PPMU, and can initiate the movement of captured data from its own multi-bank capture memory on its own high-speed Move Bus. In addition, these redundant functional blocks are supported by 1) the ability to control the analog instruments from within the test pattern, 2) the ability to dynamically assign three levels of real-time processing resources wherever they are needed, and 3) the ability to connect any pin to any instrument through the DIB Access feature.

### **Digital Capabilities for the SOC and DFT Worlds**

The Integra FLEX takes the high density CMOS technology of the J750 tester to levels of quality and throughput never before seen for SOC and DFT testing. The Integra FLEX digital instruments provide quadruple the DFT capability of the J750 (4x the scan speed and 4x the scan memory depth), and deliver the preeminent breadth of digital capability at low cost:

- 200 MHz maximum operating speed

- edge placement accuracy to ±250 ps

- 64 Meg vector memory behind each pin

- 48 single-ended pins or 24 differential pin pairs per board

- 1,056 digital pins maximum

- three drivers per pin large swing, small swing, and 50 Ohm terminated

- 100 MHz MTO with:

- 24 Meg x 64-bit Captive memory

- x, y, z address counters

- algorithmic memory pattern generator

- software-configurable fail map memory

- full high-level template support for multiple boards to one site, or multiple sites supported from one board

- 3 Gbits of SCAN data available for every 16 channels that can be configured in any way needed

- SCAN Broadcast capability for parallel test economics and longer equipment lifetime

- Digital Source and Capture (DSSC) provides serial or parallel data at 16 bits wide, with the ability to chain two DSSC blocks together for 32-bit operations

- Six (6) DSSC engines per board

- Fast keep-alive function

- Two high voltage drive pins per board

- DIB Access per four channels/pins

- PMU per pin

- per pin overvoltage/overcurrent protection that disconnects the pin electronics from the DUT on an alarm condition

Resident digital instrument features such as per-pin PMU, fast SCAN, keep-alive, memory test, and flexible configuration, work together to provide the fast throughput needed for the lowest cost digital testing. The Digital Instrument is described in *Section 5*, *Instrument Description and Specifications*.

### **Innovative Heritage**

The Integra FLEX test system draws on its J750 and Catalyst heritage, and extends their lineage with significant innovation. The Integra FLEX embodies every IP-core Teradyne technology to date and builds upon them to deliver the lowest cost, most flexible, lowest risk DFT to mixed-signal SOC test system available.

# **Section 2**

# **Meeting Test Floor Objectives**

Two of the primary design objectives for the Integra FLEX test system were to 1) enhance manufacturing utilization so that the same test system configurations would be able to accommodate peak levels as well as "normal" levels of demand, so that cost of test would be as low as possible, and 2) increase manufacturing capability so that time-to-volume would decrease, and test system capabilities would always match device test requirements.

# **Enhanced Manufacturing Utilization**

### **Per Pin Resources**

The Integra FLEX instruments are designed to provide a very high level of resources behind each pin:

- per-pin PMU on all instruments

- DIB Access, which allows any pin to be connected to any instrument, without application circuitry

- one or more on-board Time Measurement Units on each DC instrument

- on-board differential voltmeters on each DC instrument

- dual pin high voltage driver on Digital instruments

- 100 MHz self-contained Memory Test and Fail Map Memory on each Digital instrument

- six (6) independent Digital Signal Source/ Capture engines each with 128Mbit memory, per Digital instrument

- 3Gbit, totally configurable, SCAN data per 16 channels/pins on Digital instruments

- Keep-Alive function on each Digital instrument

- three LFO/mixers on Microwave instrument suite

- on-board Real-Time processor on Microwave instrument

The feature sets of the Integra FLEX instruments were designed so that, regardless of the instrument configuration on a given test system, the system would have all of the resources needed to fully support the test floor. Even what might be considered a minimal test system configuration, with several each DC and Digital instruments, has the resources for parallel, multi-site tests of continuity and leakage (via PPMUs), and rise/fall times, propagation delay, pulse width, frequency, and period (via TMUs on DC instruments), in addition to DFT techniques and full functional testing. This unprecedented level of high pin functional density offers unmatched utilization with the lowest possible cost system.

### **Configuration Flexibility**

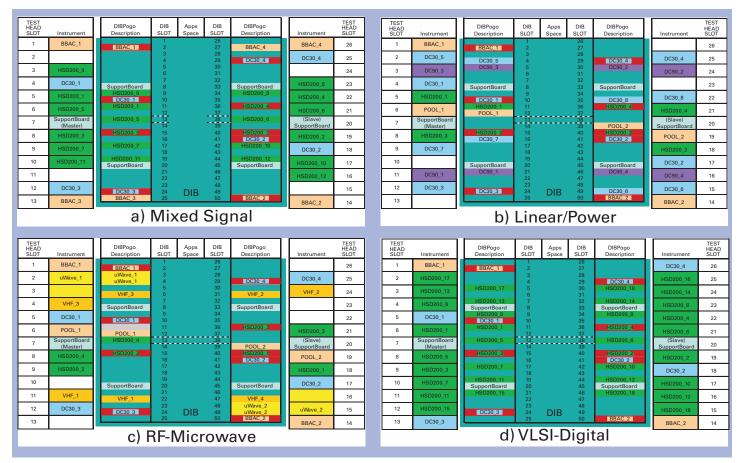

The 24 instrument slots in the Integra FLEX test head accept any instrument. This eliminates a number of constraints and significantly increases flexibility in the placement of instrument types and DIB layout. With the proper planning, instrument configurations and DIB layouts can be created that allow either 1) a single instrument suite to be configured that will test the majority of devices in a product mix, or 2) a multi-site (e.g. quad) test DIB for a single device (e.g. a mixed-signal SOC) can be used on test systems configured not only for that mixed-signal SOC device, but on Integra FLEX test systems configured primarily for linear or digital/SOC devices, with a reduction in the number of sites (i.e. dual versus quad). Figure 2-1 depicts just such a situation. Assume that a device DIB is configured for quad site testing of a mixed-signal device, as depicted in Figure 2-1(a). Some number of Integra FLEX systems on the test floor are configured for mixed-signal, linear/power (Figure 2-1(b)), RF-Microwave (Figure 2-1(c)), and VLSI-Digital (Figure 2-1(d)) devices. A surge in demand occurs for the mixed-signal device; however all of the test systems configured for mixed-signal devices are at maximum capacity.

The red highlighted DIBPogo blocks in Figure 2-1 show the common instrument slot

Figure 2-1: Enhanced manufacturing utilization

configurations among the four test system types on the test floor. The mixed-signal DIB can be used directly on any one of the other configured systems to allow testing of the mixed-signal device, at a reduced number of sites. In this way, Integra FLEX can maximize test system utilization, and minimize cost of test.

### **Performance-On-Demand**

The Integra FLEX hardware and software architectures provide for the precise matching of device test requirements and test system capability. In addition to the per pin resources of each instrument and the flexibility of configuring the test head afforded by the universal slot test head architecture, a number of performance features can be enabled (licensed) on-the-fly to precisely match test system capability with device test requirement when and where it is needed. Table 2-1 provides a list of these features and capabilities.

| Levels                                   |

|------------------------------------------|

|                                          |

| Yes/No (license)                         |

| Yes/No (license)                         |

| Yes/No (license)                         |

|                                          |

| 100, 200 MHz                             |

| 8, 16, 32, 64 M per pin                  |

| 0/1 enable                               |

| n (DSSC) 0/1 enable                      |

| 0/1 enable                               |

| 0/1 enable                               |

| Yes/No (license)                         |

| 1, 2, 4                                  |

| 1 MHz, 3 MHz, 15 MHz                     |

| 1, 2, 4, 6, 8                            |

| 1, 2, 4, 6, 8                            |

| 1, 2, 3, 4, 5, 6, 7, 8; added with sites |

| 0/1 enable                               |

|                                          |

| ±250 ps to ±1 ns                         |

| 50 MHz                                   |

|                                          |

|                                          |

|                                          |

Table 2-1: Performance Licensing

# **Increasing Manufacturing Capability**

The Integra FLEX architecture, instruments, and performance enabling to match device test requirements also contribute directly to increased manufacturing capability. The ability to provide the needed test economics in whatever configuration it is presently in, and minimize the risk associated with expanding to accommodate new devices, allows Integra FLEX to continuously deliver test capabilities matched to the needs of the test floor.

### **Elimination of Bottlenecks**

Manufacturing capability is often significantly impacted by test system architecture issues that can be categorized as "bottlenecks". A brief comparison follows between the Integra FLEX test system and the bottlenecks that typically occur in several key areas of test system architecture.

#### **Non-Pipelined Test Computer/Test System Link**

The first is the link between the test system computer and the test system itself. Even using a fiber optic channel at 800 Mbps or more to deliver multiplexed data from multiple test system instruments to the test system computer, the system suffers from the indisputable fact that all of the data has to be concentrated and sent down a single "pipeline". This places constraints on data processing, test setup and execution, and impacts overall throughput. The Integra FLEX test system architecture eliminates the single "pipeline" between the test instruments and the computing resources, by effectively moving the execution of the test program to the instruments, under precise control and coordination of the test system computer. Captured data from any given test need not be sent back to the test computer from the test head for processing, so there is no data concentration to cause a bottleneck. With no data concentration bottleneck, test execution time decreases, with a corresponding increase in throughput.

### **Background DSP/Real-Time Processing Capability**

Even test system computers that have multiple, fast CPUs are limited in how much data can be processed concurrently. This occurs *after* the data gets through the link pipeline bottleneck. This problem only increases as more sites are tested in parallel, until throughput is severely impacted, or limits are reached prematurely on the test system's multi-site testing capabilities.

The Integra FLEX test system eliminates bottlenecks due to test program processing requirements, regardless of the number of parallel test sites, with no impact on test system throughput. The Integra FLEX Background DSP/Real-Time Processing capability dynamically assigns dedicated DSP resources to each site as they are needed, or to one or more sites whose processing requirements demand more resources, as appropriate. With three levels of Real-Time Processing available to the data — at the test computer, with the addition of up to eight (8) optional Real-Time Processor modules, and on-board specific instruments — data processing limitations are eliminated, as more parallel test sites are added thereby fully supporting maximum test system throughput.

The Integra FLEX architecture that moves captured data to the Background DSP/Real-Time Processor system from the instruments also contributes significantly to eliminating a major test system bottleneck. Each Integra FLEX instrument has its own dedicated, high-speed data Move Bus to the Background DSP/Real-Time Processing system. Each instrument initiates the movement of data from its capture memory across the Move Bus at the completion of its test routine. Data processing routines for each test are stored in the Background DSP/Real-Time Processing system at test program initiation. As tests are completed and the captured data is received from the instruments, the data is processed immediately. Data processing in the Integra FLEX test system is zero-time processing, further increasing throughput.

### **Universal Instrument Slots**

Many test system architectures require that certain instrument types must reside in specific slots within the test head. This can often place severe constraints on DIB development and overall test system configurations, especially in multi-site applications. This can also impact test system reconfiguration downtime when switching from testing of one device to another. The Integra FLEX test system tester-in-the-test-head architecture provides 24 universal instrument slots, which accept any Integra FLEX instrument — AC, DC, Microwave, or Digital — for unprecedented flexibility in test head configuration and DIB development, and multi-site test support.

### **Minimized Shared Test System Resources**

The link between the test system and the test computer is the most obvious shared resource within the test system architecture. At any number of places - Pattern Generators (PatGen), data busses, clock subsystems, key functional blocks, and the instruments themselves - shared resources can impose significant constraints at one time or another during test execution. Integra FLEX instruments — AC, DC, Microwave, and Digital each have their own synchronized DDS clock, PatGen, independent capture data Move Bus, Time Measurement Units (DC instruments), PPMU (AC and Digital instruments), and a number of other functional blocks that in other test systems would be shared resources. This high functional density on each instrument contributes to the lowest possible cost of test delivered by the Integra FLEX test system, makes test development easier, and multi-site test execution more repeatable.

### **DIB Access**

Connecting two instruments such as a V/I and a waveform generator to the same DUT pins on most test systems often requires a significant amount of application circuitry including a number of signal routing relays on the DIB. This increases the complexity of the DIB, provides additional areas where critical test signals can be degraded, and uses valuable DIB real estate best reserved for DUT-specific application circuitry. Integra FLEX eliminates the need for this type of relay circuitry on the DIB because of a feature designed into every instrument referred to as DIB Access. DIB Access provides high performance signal paths that allow a primary and secondary instrument to share access to DUT pins, without the need for relays and applications circuitry on the DIB. DIB Access functionally enables any pin to be connected to any instrument.

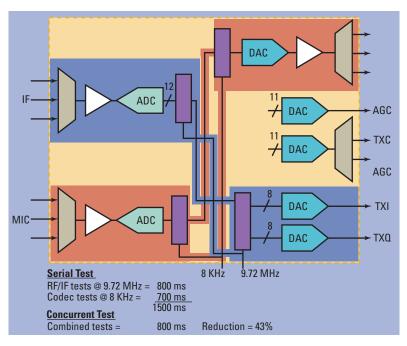

### **Pattern-Controlled Analog Instruments**

All Integra FLEX instruments — DC, AC, Microwave, and Digital — have their own independent, on-board clock, Pattern Generator, and parameter set (Pset) memory. Since instrument setups are stored locally in the Pset memory on each instrument, setup commands issued from the test computer can be broadcast to all copies of an instrument so that instrument setup for those instruments occurs simultaneously. Instrument setup instructions can be embedded in the test pattern, so as the pattern is executed on each analog instrument, those setup instructions are executed directly by the instrument, under precise timing control of the pattern. This ability significantly improves test repeatability, due to the precise timing control of the instruments from the pattern and their synchronization. Test execution time is reduced as well, since instrument setup commands execute locally from Pset memory, and need not be transmitted from the test computer each time they are required.

Each instrument initiates the movement of its captured data from its capture memory over its dedicated Move Bus to the Background DSP/Real-Time Processor system for processing. While the data from a previous test is being moved, the instrument can be setup and begin capture for the next test. This ability also reduces test execution time.

# **Section 3**

# **Improving Time-To-Market**

Integra FLEX provides both software and hardware vehicles that significantly improve time-to-market by leveraging prior investments on the production floor. The test development and execution environment plays a critical role in that leveraging ability, and is discussed here within that context. Please refer to *Section 4*, *Multi-Level Test Development: IG-XL 5.0* for more detailed information.

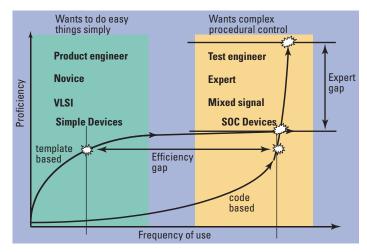

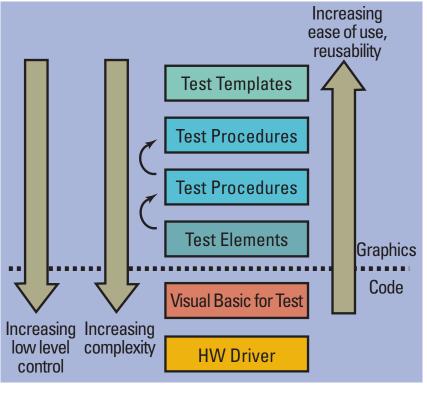

## **Unrestricted Test Development**

Complex devices require complex test programs. Test systems that don't leverage the expertise of more experienced test engineers for use by less experienced ones, create a bottleneck in the test development effort, and waste prior expenditures in development time and effort. Test development environments that do not provide both intuitive graphical test development tools as well as code-based tools, create a test development bottleneck by forcing every test engineer, regardless of experience level, to learn the test system coding language. This places significant constraints on lessexperience test engineers who need to make as important a contribution to time-to-market and time-to-volume as their more experienced colleagues. The Integra FLEX IG-XL 5.0 test development and execution environment eliminates these barriers by providing a hierarchy of test development tools that range from simple, graphically-based templates, to extremely powerful code-based program development. Integra FLEX test programs are fully supported by the concept of "develop once and reuse often". Test templates, elements, and procedures developed by one test engineer can be fully documented using integral HTML Help documentation generation tools so that another engineer can quickly understand how to use them for their own development efforts. Test templates, elements, and procedures developed by test engineering

are appended to the extensive library of predeveloped and proven test procedures supplied with the Integra FLEX test system. In this way, prior test development effort is fully leveraged for the program under development.

# Precision Synchronized Cross-Domain Debugging

Devices with disparate functional blocks require concurrent testing in order to guaranteed device performance and freedom from interaction among those functional blocks. If the test system cannot fully "line up" all digital and analog events at the precise time of a test failure, the test engineer is virtually guaranteed extended test debug time and effort. The inability of a test system to adequately provide completely synchronized event information, across all instrument types — AC, DC, Microwave, and Digital at any point in the execution of a test program, can be a significant bottleneck in test development and debug. Integra FLEX overcomes this test debug bottleneck because of the Integra FLEX TimeTrack<sup>TM</sup> system. TimeTrack is the combination of the per instrument architectural elements (i.e. clock, PatGen, Pset memory, etc.) and the debugging tools within the IG-XL 5.0 test development environment, which when taken together provide this capability. The TimeTrack precision phase alignment capability is built-in to the Integra FLEX instruments, and enabled by the TimeTrack tools supplied as part of the Integra FLEX IG-XL 5.0 test development and execution environment. TimeTrack enables all Integra FLEX instruments — AC, DC, Microwave, and Digital - to respond to Halt-On-Failure signals from any other instrument, and for the debug software to "know" their precise position in their respective test patterns, so that every event at the precise point of failure can be "lined up", and analyzed, in context, as quickly as possible.

# **Integrated Tools**

Integra FLEX and IG-XL 5.0 provide a suite of integrated tools to support design-to-test pattern translation, test simulation, and DFT. For a detailed list of Teradyne's working partners in design-to-manufacturing solutions, please refer to *Section 4*, *Multi-Level Test Development: IG-XL 5.0*.

# Simplified Docking and Production Integration

A significant amount of effort has gone in to the physical design of the Integra FLEX so that the investments made in proven solutions for previous platforms are completely leveraged for use with Integra FLEX. Special effort relative to mechanical docking issues and interfaces for probers and handlers allow Integra FLEX to fully leverage these time and resource-intensive expenditures in order to minimize their impact on time-tomarket.

Table 3-1 lists the probers and handlers for which Integra FLEX interface solutions are currently available.

### Integra FLEX/Catalyst Prober Interface Configurability

Integra FLEX prober interfaces are configurable with Catalyst prober interfaces. The Catalyst L-Plate is removed and permanently replaced with a no-charge Integra FLEX/Catalyst compatible L-Plate. Two course alignment pins, three Kinematic dock grooves, and three groove spacers are removed from the Catalyst L-Plate and reused on the Integra FLEX L-Plate. Five additional parts are required to complete the Integra FLEX/Catalyst Prober Interface upgrade. After the upgrade, moving between the Catalyst and Integra FLEX involves an exchange of the Tower/Flange assembly, and the removal or addition of a Quick DIB Clamp Plate (QDC) as required.

### Integra FLEX/Catalyst Handler Interface Configurability

Integra FLEX handler interfaces are configurable with Catalyst handler interfaces. The Catalyst Handler plate, insert, and three groove spacers are removed and permanently replaced with a no-charge Integra FLEX/ Catalyst compatible Handler plate, insert, and v-grooves. Four additional parts are required to complete the Integra FLEX/ Catalyst Handler Interface upgrade. After the upgrade, moving between the Catalyst and Integra FLEX involves an exchange of the HIB insert, and the removal or addition of a Quick DIB Clamp Plate (QDC) as required.

### Integra FLEX/J750 Interface Configurability

Integra FLEX interfaces are planned to be configurable with J750 interfaces. Please refer to separate product roadmap documents for a schedule of availability.

### Handler/Prober Communications

GPIB drivers exist for most handlers and probers. The serial driver supports IEEE-P849 protocol, while the parallel TTL driver supports 32, 64, or 96 I/O ports. GPIB interfaces can be mounted in the Auxiliary Equipment Cabinet. KLA Integrator support is included, which allows job load and data collection using the Prober control panel.

### Available Interface Solutions

| Probers                              |

|--------------------------------------|

| EG 40XX Top and Bottom Load          |

| EG 5300 Top and Bottom Load          |

| TEL P8XL Top and Bottom Load         |

| TEL P12XL Top and Bottom Load        |

| TSK UF200 AL Top Load                |

| TSK UF200 FL Bottom Load             |

| TSK UF200S Bottom Load               |

| TSK UF200/APM 90 Top and Bottom Load |

| TSK UF300 Top and Bottom Load        |

| Handlers                             |

| DeltaFLEX                            |

| Delta Castle                         |

| Seiko-Epson NS5000/NS6000            |

| Synax 1701                           |

| Synax 1121                           |

|                                      |

Table 3-1: Integra FLEX interface

# **Section 4**

# **Multi-LevelTest Development: IG-XL 5.0**

# **Key Objectives**

From the onset, it was clear that the test development environment necessary to support the flexibility and breadth of application of the Integra FLEX test system must itself be highly flexible and address a breadth of concerns and issues spanning diverse environments:

- Test/Product Engineer Background

- Senior versus junior

- Digital versus mixed-signal

- Specific device applications

- · Specific test platform

- Business Model

- Integrated Device Manufacturer (IDM)

- Fabless

- Contract manufacturer/test house

- Available Resources

- Test program converted from similar test platform versus different platform

- Test program converted with test waveforms, procedures, DSP algorithms, etc. available

- New design, platform, and application

- Design and Process

- Design well known, already in production versus new design

- Design is merge of IP cores from various design companies (IDM, fabless, etc.)

- Well-controlled process versus new process

Figure 4-1: Diversity of test environments

From these concerns and issues, three prime objectives were identified that the Integra FLEX test development environment must meet:

- Extend the J750 IG-XL software to provide a common platform for the entire Integra family of general-purpose testers

- Provide a multi-level programming capability to accommodate a diverse development environment, and enable a shorter development time

- Provide an advanced linear and mixedsignal use model and toolset to build on the DUT-centric test development environment of IG-XL

The result of achieving these three objectives is the device-oriented programming and debug environment embodied by Integra FLEX IG-XL 5.0.

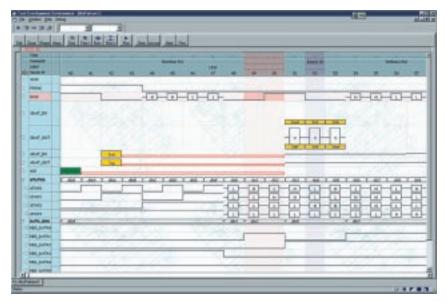

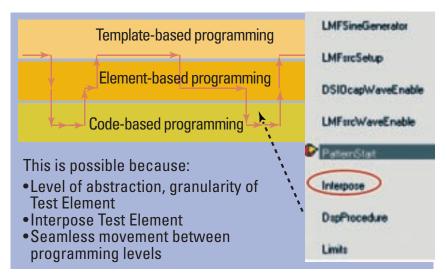

# **Multi-level Programming Capability**

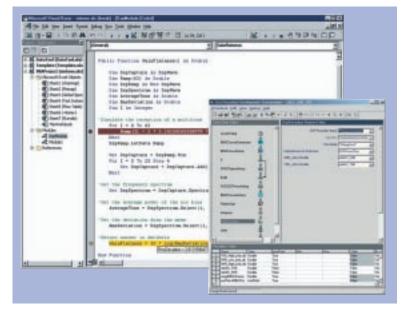

Integra FLEX IG-XL 5.0 is built upon the foundations of Teradyne J750 IG-XL, which carries forward key concepts from IMAGE, and represents a community of several thousand users, and a combined development effort of over 730 person-years of engineering. From that experience base, Integra FLEX IG-XL 5.0 provides a test development environment that allows both highly experienced and novice programmers alike to rapidly develop fully functional test programs from an intuitive, graphical user interface, based on the Microsoft Excel® spreadsheet paradigm. In its simplest form, device specifications, timing, levels, and edges are entered into pre-formatted test templates, and the fully functional test program is generated from the filled in templates. In a manner of minutes, a novice can have a verified test program ready to run, without learning any of the Integra FLEX programming language. Refer to Figure 4-2. At its most complex, an experienced programmer can re-use previously developed test templates and elements, flow them together to create a procedure, write code-

Figure 4-2: Programming levels

Figure 4-3: Seamless integration of programming levels

based routines that are then selected from template pull-down menus to become part of that procedure (or any other), to create a test program for a mixed-signal SOC device. IG-XL 5.0 provides an environment where all test development can remain within the graphical user interface, unless custom device issues or the augmentation of test functionality require code-based development. Refer to Figure 4-3.

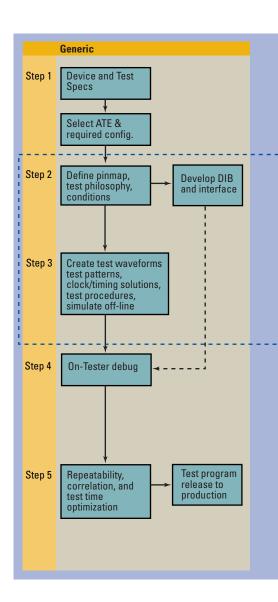

The general approach to programming within the IG-XL 5.0 environment is the entry of device data in an enhanced spreadsheet. The flexibility of IG-XL 5.0 allows both fixed numbers as well as equations with variables to be entered into device parameters, allowing the rapid development of relational test parameters such as might be used for range or limit testing. Device pin names and timing relationships are entered into the spreadsheet, and the software determines how best to configure the instruments to support that timing relationship, within the capabilities of the test system. Should a set of device parameters or timing relationship be defined that cannot be

Figure 4-4: Generic vs. IG-XL 5.0 test development flow

supported by the test system with full accuracy and performance, the programmer receives immediate feedback, so that any required adjustments can be made. In this way, the programmer need only think about the device under test, and not the test system.

As experienced programmers code and build custom, complex, template-based test elements, routines, and procedures, they have the tools available to automatically generate HTML help documentation, with tool tips, to guide less experienced programmers in their setup and use. This system-generated help documentation, along with library functions, is one of the features of IG-XL 5.0 that enables a "design once, reuse many times" approach to the test program development process. Recognizing that programmers may come to the Integra FLEX IG-XL 5.0 environment with a variety of platform experience, IG-XL 5.0 features a standardized, familiar interface that is consistent with industry practice.

## **Device-centric Test Development**

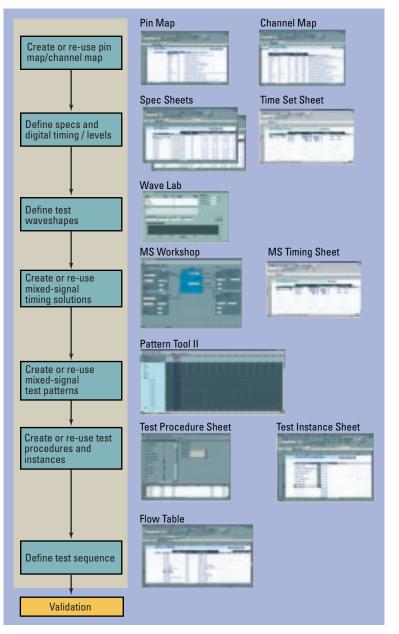

### General DataTool<sup>™</sup> Overview

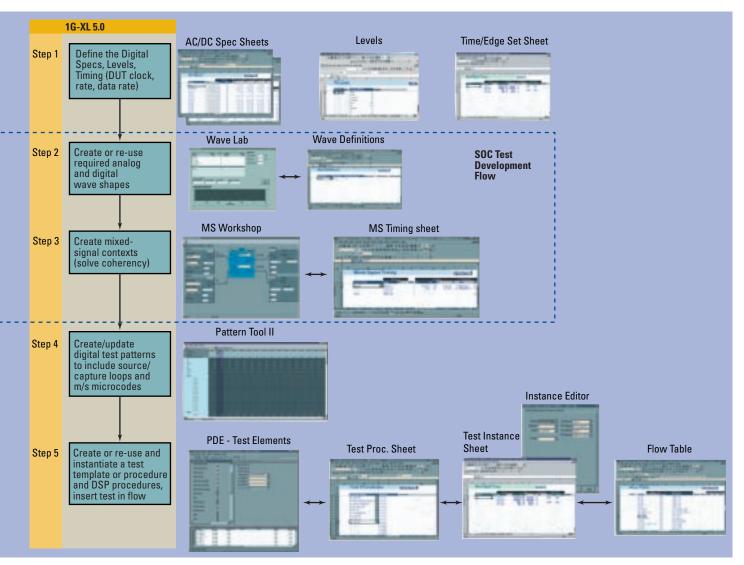

Figure 4-4 illustrates the difference in the overall test development flow between a tester-centric approach and the Integra FLEX device-centric approach, and provides a glimpse of the tools available to enable that development to occur in the shortest possible time. As is readily apparent, each of the steps and the tools used to support them all define their required data in terms of device specifications and parameters. Existing test elements and procedures are re-used either as is, or

Figure 4-5: IG-XL 5.0 workbook architecture

instances of those elements and procedures are quickly and simply created to satisfy the specific device requirements.

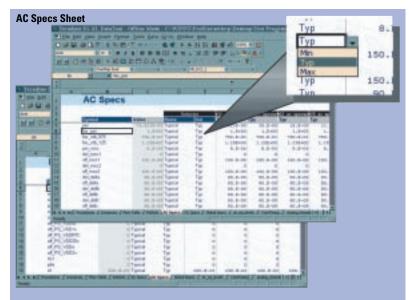

The device data is organized into the following general categories:

- Pinmap

- Tester Channel Map

- Device Specs (AC & DC)

- Timing and Formatting (based on device specs)

- DC and Pin Levels (based on device specs)

- Test Instances (based on templates and procedures)

- Mixed-Signal Test Waveforms and Setups

- Digital and Mixed-Signal Patterns

- Program Flow and Binning

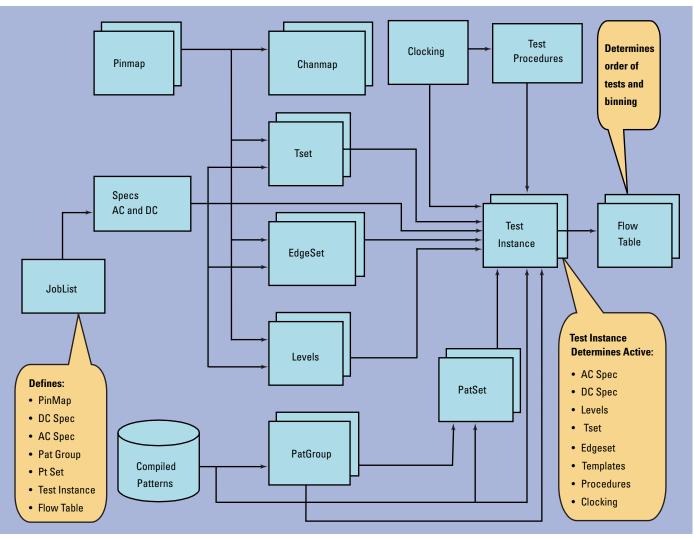

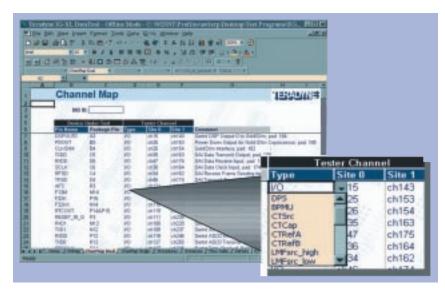

Figure 4-5 depicts the overall test flow block diagram, and how the various device data and their respective spreadsheet tools within the DataTool environment interrelate. Each is briefly described below. Those spreadsheets and tools specific to digital and mixed-signal development are described in the following sections. The descriptions below assume that the test program is being built and debugged for a single (first) site (Site 0). Multi-site capability is added by duplicating worksheet columns for N additional sites. All tools and templates adapt automatically to multiple sites. Please refer to the later section *Native Multisite Capabilities* for more information on IG-XL V5.0 multi-site capabilities.

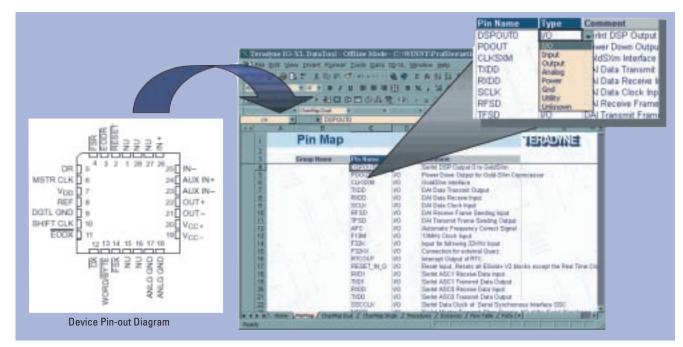

### **Pin Map**

The Pin Map Sheet (refer to Figure 4-6) provides a worksheet for entering the names of the device pins as they are defined on the device pin-out diagram. A pop-up menu allows rapid definition of the type of pin, (i.e. I/O, input, output, analog, power, etc.). Comments regarding the pin function are entered as well. The Pin Map defines the interface to the device, in device terms.

Figure 4-6: Pin map worksheet

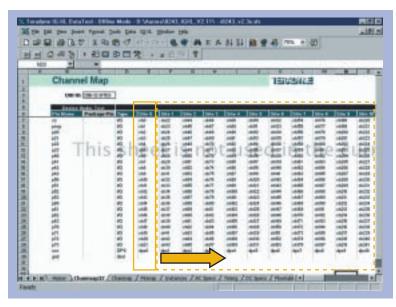

Figure 4-7: Channel map worksheet

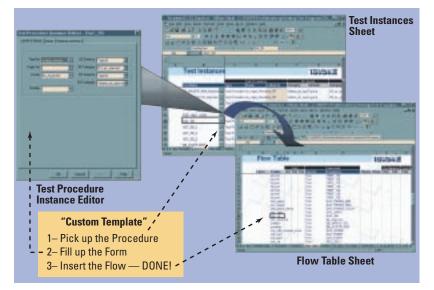

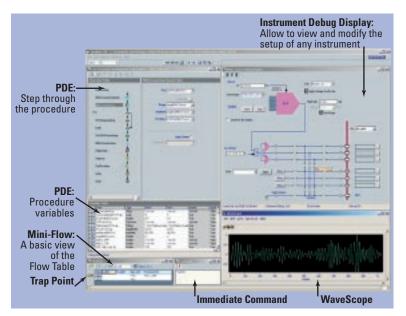

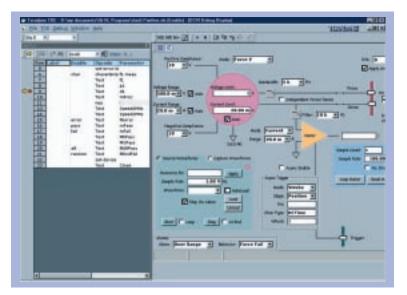

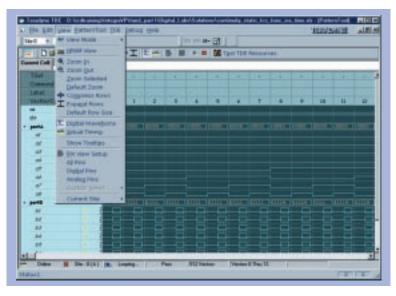

### **Channel Map**